# Design and Simulation of Quadrature Phase Detection in Electrical Capacitance Volume Tomography

## Imamul Muttakin\*, Arbai Yusuf, Rohmadi, Wahyu Widada, Warsito P. Taruno CTECH Labs Edwar Technology

JI. Jalur Sutera Kav. Spektra 23 BC No. 10-12 Alam Sutera, Tangerang, Banten, Indonesia \*Corresponding author, e-mail: imuttakin@c-techlabs.com

## Abstract

Capacitance measurement accuracy is affected by phase conformity between signal and reference. This work describes phase detection scheme which is necessary for phase synchronization in tomography application. Core processing for calculating phase and amplitude of the detected signal was built on FPGA (Field-Programmable Gate-Array) platform. Phase shift demodulation algorithm employs IP core provided by Xilinx FPGA. Direct digital synthesizer (DDS), multiplier, accumulator, and CORDIC (coordinate rotation digital computer) modules were used as excitation-reference signal generator, signal multiplication, accumulation, and conversion to polar coordinate in order to conduct trigonometric operation respectively. Hardware design was emulated on MATLAB-Xilinx System Generator to observe its performance. Phase detection range 0-114.58° and mean absolute error 0.58° have been achieved. Data processing rate solely at digital signal stage was approximately 100data/s suitable for 32-channel electrical capacitance volume tomography (ECVT) system.

Keywords: quadrature demodulation, phase detection, system generator, FPGA, ECVT

## 1. Introduction

Phase detection is one of the most important feature in data acquisition system for electrical capacitance volume tomography (ECVT). ECVT is a volumetric (real-time 3D) tomography technique based on capacitance measurement which has replaced classical system in two-dimensional slicing for tomography imaging [1]. The former electrical capacitance tomography (ECT) method basically utilizes sensitivity of certain capacitive sensor configuration to map permittivity distribution in the object space. It is a non-radiation, non-invasive, and low-cost system which has been widely used in petro-chemical process industry as well as medical applications [2]. However, this modality comes with ill-posed inverse problem as natural characteristic of similar soft-field tomography e.g. optical molecular imaging [3] hence advancement in image reconstruction algorithm and hardware design are significant.

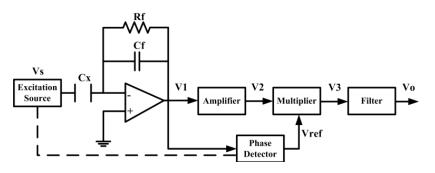

Data acquisition system collects data obtained from sensor to be formed and sent to computer which manipulates the data pattern into image using specific algorithm. In the well-known circuitry for capacitance to voltage (C-V) conversion, measurement accuracy is affected by phase conformity between output C-V signal and reference signal. This circumstance makes phase tracking necessary for system's reliability to reduce phase error [4]-[5]. Figure 1 shows a lock-in mechanism in front of C-V circuit to extract information from measured capacitance.

Figure 1. Capacitance to voltage circuitry with lock-in mechanism

According to Figure 1, if both  $V_{ref}$  and  $V_2$  signals have identical phase,  $V_o$  will only related to amplitude of input signals. However, practically two signals added into lock-in will generate additional phase difference which decreases output amplitude and causes measurement error. The additional phase difference is relevant toward stray capacitance, and different stray capacitance brings different phase angle. Therefore, phase shift will impose certain error. By using coherent demodulation to detect the signal with phase tracer circuit, this kind of problem can be well addressed. Consequently, multiplier output will reach maximum, circuit is stray-immune, in the same time sensitivity and stability of the system can be improved [4].

Performance improvement will be achieved by implementing most functionality into digital hardware rather than analog. Field-Programmable Gate-Array (FPGA) is employed as control processing core, excitation signal generation, and signal demodulation. The modular design of FPGA produces minimal hardware overhead, is flexible, fast, and stable in order to facilitate further development of measurement system.

## 2. Capacitance Measurement

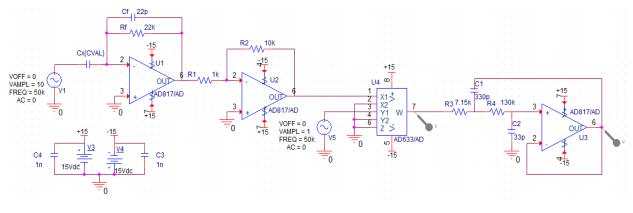

The ac-based capacitance measurement circuit schematic is shown in Figure 2.

Figure 2. Schematic of ac-based capacitance measurement circuit

From the circuit, absolute capacitance value can be obtained using equation,

$$V_{out}(DC) = \frac{1}{2} \left[ \left( \frac{C_x}{C_f} \right) \left( \frac{R_2}{R_1} \right) \left( \frac{V_{ref}}{k} \right) \right] V_{in}$$

(1)

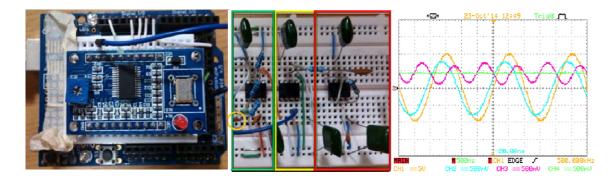

where  $C_x$  is measured capacitance,  $C_f$  is charge-amplifier feedback capacitance,  $R_1$  and  $R_2$  are feedback gain, and k is multiplication factor. For the implementation, chip Direct Digital Synthesizer (DDS) AD9850 was used as waveform generator controlled by Arduino to set sinusoidal signal of certain frequency. Capacitance measurement circuit and gain AD817 (green box), multiplier AD633 (yellow box), and low-pass filter LTC1062 (red box) along with respective output signals are depicted in Figure 3 below.

Figure 3. Analog DDS waveform generator (left); capacitance measurement circuit (center); output signals (right)

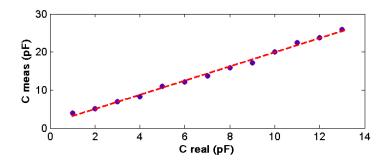

Experiment results were observed on oscilloscope to analyze output of each stage for the given measured capacitance value. Referring to the Figure 3 (right), yellow trace signal is DDS waveform, blue trace is output of C-V converter plus inverting gain, red trace is multiplier's output, and green trace is filtered output signal. Final DC voltage was converted into capacitance value using (1) and compared with real capacitance test value from 1pF-13pF as in Table 1 and plotted in Figure 4.

| 4 | Vo (V) | C real (pF) | C meas (pF) |

|---|--------|-------------|-------------|

|   | 0.356  | 1           | 3.916       |

|   | 0.465  | 2           | 5.115       |

|   | 0.627  | 3           | 6.897       |

|   | 0.751  | 4           | 8.261       |

|   | 1      | 5           | 11          |

|   | 1.1    | 6           | 12.1        |

|   | 1.24   | 7           | 13.64       |

|   | 1.44   | 8           | 15.84       |

|   | 1.56   | 9           | 17.16       |

|   | 1.82   | 10          | 20.02       |

|   | 2.04   | 11          | 22.44       |

|   | 2.16   | 12          | 23.76       |

|   | 2.36   | 13          | 25.96       |

Figure 4. Measured capacitance vs real capacitance value

It can be seen in Table 1, there are differences between measured capacitance values and real capacitance values. Nevertheless, Figure 4 shows measurement's linear trend with Rsquare 0.995 and level of confidence 95%. The accuracy problem occurs because of phase inconformity between ac measurement output signal and multiplicator reference signal. So, phase synchronization of signals should be conducted in order to obtain accurate capacitance measurement value. As initial step, phase detection mechanism is necessary. The following

Design and Simulation of Quadrature Phase Detection in Electrical .... (Imamul Muttakin)

sections will explain hardware design for quadrature phase detection algorithm which has been presented in [6].

## 3. Quadrature Demodulation

Modulation and demodulation techniques regarding signal's phase information are commonly found in communication theory. Various modulation principle with its performance analysis and algorithm for digital phase modulation are described in [7] and [8] respectively. In phase detection, sine signal needs to be demodulated with measured parameter. Digital demodulation makes use of reference signal generated from DDS to digitally modulate measured signal to obtain its amplitude and phase.

$$u(n) = A \sin\left(\frac{2\pi}{N}n + \theta\right); i(n) = \sin\left(\frac{2\pi}{N}n\right); q(n) = \cos\left(\frac{2\pi}{N}n\right)$$

$$R = \sum_{n=0}^{N-1} i(n) \cdot u(n) = \sum_{n=0}^{N-1} \sin\left(\frac{2\pi}{N}n\right) \cdot A \sin\left(\frac{2\pi}{N}n + \theta\right) = NA\frac{1}{2}\cos\theta$$

$$I = \sum_{n=0}^{N-1} q(n) \cdot u(n) = \sum_{n=0}^{N-1} \cos\left(\frac{2\pi}{N}n\right) \cdot A \sin\left(\frac{2\pi}{N}n + \theta\right) = NA\frac{1}{2}\sin\theta$$

$$Z = \sqrt{R^2 + I^2}; \theta = \tan^{-1}\frac{I}{R}$$

(2)

This syncronous modulation and demodulation (PSD, also known as phase shift demodulation) has high precision and adaptation level based on matched filter theory which is linear time-invariant by maximizing signal-to-noise ratio (SNR). Considerations in PSD are: input signal frequency and phase must be similar, reference signal should be justified accurately, anticipate phase shift because of stray capacitance and resistance channel, and degradation of SNR due to frequency difference between driving signal and reference signal.

Demodulation is accomplished through several steps. First, phase difference between digitized reference signal and measured signal is identified. Second, delay the reference signal with specific number from sampling period according to phase difference value obtained from preceding step to match reference signal's phase with measured signal's phase. Last, multiply the measured signal with adjusted reference signal in one sine wave period and then accumulate the results accordingly [9].

Integration of DDS and PSD module into single FPGA hardware improves systematic SNR dan simplifies peripheral circuits. For real-time processing, large amount of data on frontend with high-speed and relatively simple pre-processing architecture are suitable for FPGA implementation [10].

## 4. Hardware Design Method

As an alternative to popular approaches toward FPGA programming [11], this work relies on hardware-software co-design strategy. Phase detection algorithm i.e. phase shift demodulation is built using Xilinx FPGA IP core. DDS, multiplier, accumulator, and CORDIC are functioned as excitation-reference signal generation, signal multiplication, accumulation, and conversion to polar coordinate in order to conduct trigonometric operation respectively.

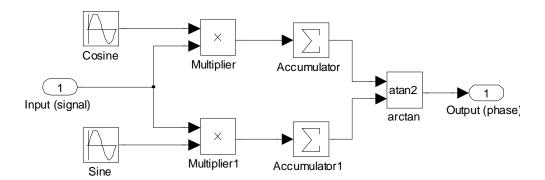

Figure 5. Quadrature phase detection scheme

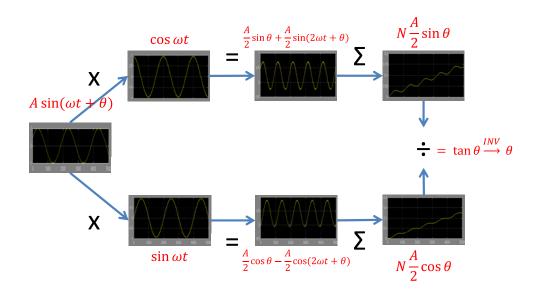

Block diagram in Figure 5 represents signal flow (contains phase shift) with quadrature demodulation mechanism, where accumulation results will be brought to inverse tangent calculation to obtain phase output value. Equation identity of multiplication between sine with sine and sine with cosine also division sine-cosine is elaborated in (3).

$$A\sin(\omega_{1}t+\theta) \times \sin(\omega_{2}t) = \frac{A}{2}\cos((\omega_{1}-\omega_{2})t+\theta) - \frac{A}{2}\cos((\omega_{1}+\omega_{2})t+\theta)$$

$$A\sin(\omega_{1}t+\theta) \times \cos(\omega_{2}t) = \frac{A}{2}\sin((\omega_{1}-\omega_{2})t+\theta) + \frac{A}{2}\sin((\omega_{1}+\omega_{2})t+\theta)$$

$$\tan\theta = \frac{\sin\theta}{\cos\theta}$$

(3)

Therefore, phase can be extracted if the detected signal is multiplied with reference sine and cosine signal, both of which have identical frequency. Sum frequency component is then eliminated by accumulating multiplication result. As been known, accumulation of symmetrical signal with zero offset will produce zero mean value so that the sum frequency component signal will vanish from equation. In the end, with division operation tangent phase angle will be obtained and then the inverse is phase value. Those division and inverse mechanism are conducted after conversion into polar domain using CORDIC operation.

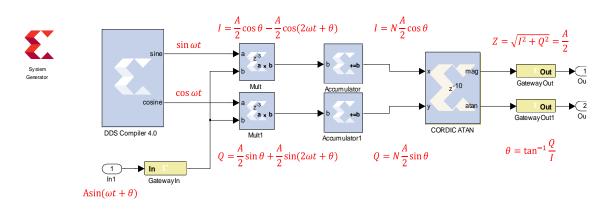

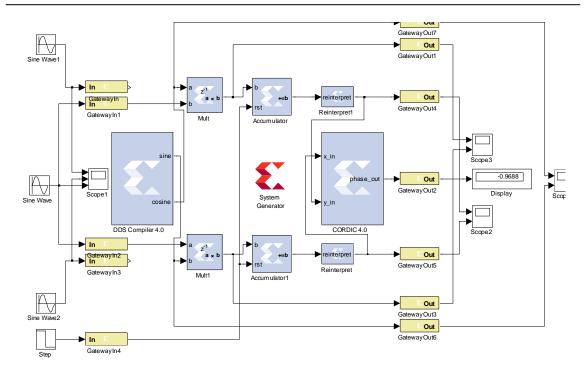

Implementation of the mechanism on Xilinx System Generator is described in Figure 6.

Figure 6. Xilinx System Generator core block

whereas, signal flow is depicted in Figure 7 below.

Figure 7. Quadrature phase detection signal flow

Synchronous sine and cosine signal produced by DDS IP core implemented in FPGA are directly used in digital domain for demodulation. Compared with conventional analog demodulation, the method can eliminate the possibility of frequency mismatch and phase variation between signals. Computation process is conducted in dedicated modules (multiplier-accumulator) and avoiding data buffer so that digital demodulation can be performed online in order to maximize acquisition rate. Consquently, it will introduce a relatively simple system with better reliability [12].

## 5. Simulation Result

Hardware-software co-simulation using MATLAB-Xilinx System Generator allows to design and observe the characteristics of hardware; on the other hand manipulate the input signal and process the output signal by software. Fixed-point number will be used to maintain consistency with practical running process in digital device [13].

## 5.1. MATLAB Xilinx System Generator

The development issues in hardware design using MATLAB Xilinx System Generator comprises: 1) determining design specification, 2) designing a system in Simulink utilizing System Generator blocks, 3) simulating the design, 4) generating hardware description language (HDL) code, 5) implementing HDL code into target hardware [14]. Step 1 through 3 were applied to foresee system's performance and capability for further ECVT development.

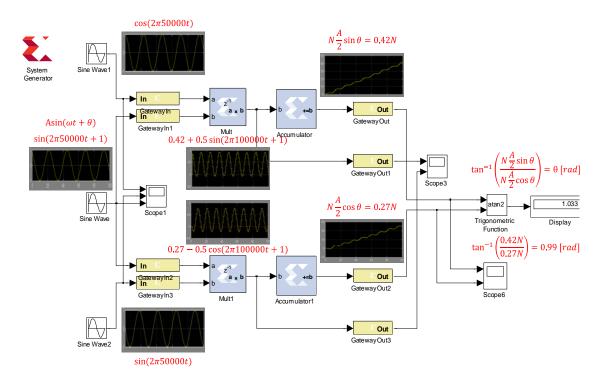

Figure 8. Implementation of Xilinx IP core for quadrature demodulation

Implementation result of Xilinx IP Core multiplier and accumulator for quadrature demodulation calculation is shown in Figure 8. In the system, input sine signal 50kHz (chosen operation frequency) is applied with phase shift 1 radian. Hardware multiplier then multiply the signal with each of reference sine and cosine signal where the frequency is set similar to the input signal. Each multiplication result is brought into hardware accumulator to be accumulated thus high frequency component will be eliminated and accumulation of phase function will remain. Trigronometric operation *atan2* (two-input inverse tangent) is applied using MATLAB function. On the display, phase value (in radian) is shown.

### 5.2. System Overview

Overview of the system for phase shift demodulation implemented on Xilinx System Generator is shown as following Figure 9.

Figure 9. Quadrature phase detection system overview

From the design, system specification that can be provided is formulated in Table 2.

| Table 2. System Specification |             |                            |             |  |  |

|-------------------------------|-------------|----------------------------|-------------|--|--|

| Operational Frequency         |             | 50kHz                      |             |  |  |

| Phase Detection Range         |             | 0-114.58° / -57.29°~57.29° |             |  |  |

| Res=8-bit;                    | Res=16-bit; | Res=8-bit;                 | Res=16-bit; |  |  |

| Clk=100MHz;                   | Clk=100MHz; | Clk=200MHz;                | Clk=200MHz; |  |  |

| MAE=0.8529°                   | MAE=0.5794° | MAE=3.6494°                | MAE=3.9960° |  |  |

| Data Proc.                    | 1785 data/s | 416 data/s                 | 100 data/s  |  |  |

| Rate                          | (8Ch)       | (16Ch)                     | (32Ch)      |  |  |

Equation (4) and (5) were used to derive data rate and mean absoulte error (MAE) respectively,

$$Throughput = \frac{f_{clk}}{\frac{f_{ADC}}{f_{op}}N_{period}\frac{n(n-1)}{2}}$$

(4)

$$MAE = \frac{1}{N}\sum_{i=1}^{N}|f_i - c_i|$$

(5)

where  $f_{clk}$ =hardware clock;  $f_{ADC}$ =ADC sampling rate;  $f_{op}$ =operational frequency;  $N_{period}$ =number of signal period; n=measurement channel; N=number of data;  $f_{r}$ =theoretical value;  $c_{r}$ =measured value.

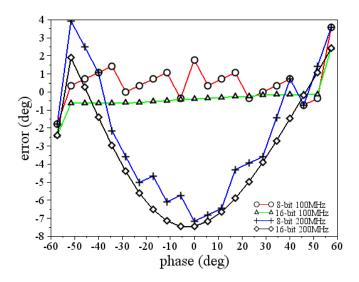

Figure 10. Measurement error plot

Measurement error is plotted in Figure 10 showing the most linear result at 16-bit data and 100MHz clock frequency.

### 6. Conclusion

Core processing for calculating phase and amplitude of the detected signal was designed on FPGA platform. Hardware-software co-simulation using MATLAB-Xilinx System Generator allows to design and observe the characteristics of hardware; on the other hand manipulate the input signal and process the output signal by software. To perform hardware test with real input and output, the design needs to be downloaded onto FPGA and connected with external blocks.

The optimum system design, adjusted to 16-bit data resolution and clock speed 100MHz, gives phase detection range 0-114.58° (or  $\pm 57.29^{\circ}$ ) and mean absolute error 0.58°. Data processing rate solely at digital signal stage is approximately 1785data/s (for 8-channel), 416data/s (for 16-channel), and 100data/s (for 32-channel).

#### Acknowledgment

Authors would like to thank researchers of CTECH Laboratories, Edwar Technology (www.c-techlabs.com) who have helped in experiment. Our appreciation also goes to reviewers, committee and panelists in the International Conference on Electrical Engineering, Computer Science and Informatics 2014 (EECSI 2014) for their valuable comments and suggestions to improve this paper.

#### References

- [1] Warsito W, Marashdeh Q, Fan LS. Electrical Capacitance Volume Tomography. *IEEE Sensors Journal*. 2007; 7(4): 525-535.

- [2] Jiang P, Fan S, Xiong T, Huang H. Investigation on the Sensitivity Distribution in Electrical Capacitance Tomography System. *TELKOMNIKA Indonesian Journal of Electrical Engineering*. 2013; 11(12): 7088-7093.

- [3] Alali A. Automatic Segmentation Framework of Building Anatomical Mouse Model for Bioluminescence Tomography. *TELKOMNIKA Indonesian Journal of Electrical Engineering.* 2013; 11(9): 4997-5004.

- [4] Zhang H, Ren D, Du LM. A new improved data acquisition system for electrical capacitance tomography. *Advanced Materials Research*. 2013; 756-759: 1527-1531.

- [5] Zhang X, Wang H. *Digital phase-sensitive demodulation in electrical capacitance tomography system.* 7th World Congress on Intelligent Control and Automation (WCICA). 2008: 6730-6733.

- [6] Muttakin I, Yusuf A, Rohmadi, Widada W, Taruno WP. *Hardware Design for Quadrature Phase Detection Algorithm in ECVT*. Proceeding of the 2014 International Conference on Electrical Engineering, Computer Science and Informatics (EECSI). 2014: 232-235.

- [7] Guo-Hui W, Ji-Yang D, Bao-Jun C. The Research on Telemetry Modulation System. *TELKOMNIKA* Indonesian Journal of Electrical Engineering. 2013; 11(5): 2342-2350.

- [8] Jun-Suo Q. A Algorithm of Fast Digital Phase Modulation Signal Recognition. *TELKOMNIKA Indonesian Journal of Electrical Engineering*. 2012; 10(8): 2330-2335.

- [9] Zhou H, Xu L, Cao Z, Xu C. An alternative digital multiplication demodulation method for electrical capacitance tomography. IEEE International Instrumentation and Measurement Technology Conference (I2MTC). 2012: 1204-1209.

- [10] Zhang X, Wang H, Cui Z, Tang L. A Novel ECT System Based on FPGA and DSP. Second International Conference on Innovative Computing, Information and Control (ICICIC). 2007: 510-513.

- [11] Sutikno T, Idris NRN, Jidin AZ. Overview on Strategies and Approaches for FPGA Programming. *TELKOMNIKA Indonesian Journal of Electrical Engineering*. 2014; 12(2): 273-282.

- [12] Wang H, Cui Z, Xu Y, Zhang L, He Y. *Digital signal processing in electrical capacitance tomography*. IEEE Asia Pacific Conference on Circuits and Systems (APCCAS). 2008: 465-468.

- [13] Xu L, Zhou H, Cao Z, Yang WQ. A Digital Switching Demodulator for Electrical Capacitance Tomography. IEEE Transactions on Instrumentation and Measurement. 2013; 62(5): 1025-1033.

- [14] Ownby M, Mahmoud WH. A design methodology for implementing DSP with Xilinx® System Generator for Matlab®. Proceedings of the 35th Southeastern Symposium on System Theory. 2003: 404-408.

64 🔳