# Parallel Connected VSI Inverter Using Multi-Carrier **Based Sinusoidal PWM Technique**

D. Karthikeyan<sup>\*1</sup>, R. Palanisamy<sup>2</sup>, K. Vijayakumar<sup>3</sup>, A. Velu<sup>4</sup>, D. Selvabharathi<sup>5</sup> <sup>1,2,3,5</sup>Department of EEE, SRM University, Chennai, India

<sup>4</sup>Navodaya Institute of Technology, Raichur, India

\*Corresponding author, e-mail: kathipncl@gmail.com<sup>1</sup>, krspalani@gmail.com<sup>2</sup>,kvijay\_srm@rediffmail.com<sup>3</sup>, velu.inventions@gmail.com<sup>4</sup>, dspsrm@gmail.com<sup>5</sup>

# Abstract

This paper explains the simulation and modelling of Parallel operation of VSI inverter using multicarrier based PWM technique. By this proposed method three level inverter output voltages generated instead of using multilevel inverter or two level dual VSI inverter. This system employs single dc voltage source, which gives supply to both VSI inverter by using parallel connection. The multi-carrier based pulse width modulation technique affianced to control the inverter power switches. The proposed system offers improved output voltage, better current control and reduced harmonic distortion. The simulation results of this proposed system was verified using matlab/simulink.

Keywords: pulse width modulation (PWM), multi-carrier PWM (MC-PWM), parallel VSI inverter, modulating frequency

# Copyright © 2017 Universitas Ahmad Dahlan. All rights reserved.

# 1. Introduction

Due to rapidly increasing energy demand in industrial and domestic applications, the switching loss and power loss in the power electronic system can be minimised with proper switching strategy [1]. The inverter is used to convert the dc source into ac output, which is mainly applied for variable frequency drives [2]. Two level inverter has disadvantages are voltage stress, switching loss, required separate dc-dc boost converter and harmonic content [3,4]. These demerits are rectified by using the multilevel converters and the three level output waveform can obtained by connecting the two 2-level VSI inverter in parallel as an alternative of using the multilevel topologies [5]. The various multilevel topologies are neutral point clamping, cascaded H-bridge and flying capacitor used for medium voltage and high power applications. The parallel VSI inverter utilised single dc source for producing 3-level output voltage [6,7].

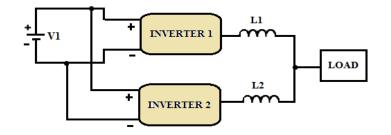

The multilevel topologies place a vital responsibility in renewable application, battery cells, fuel cells and other sources [8,9]. But in various disadvantages of multilevel topologies are capacitor balancing problem, common mode voltage, voltage stress, number of dc sources, conduction loss and complexity in PWM control strategies are remedy by using parallel connected VSI inverter with single source system [10]. The general block diagram for parallel connection of inverter is shown in Figure 1.

Figure 1. General block diagram for parallel operation of inverter

The different PWM control methodologies are implemented for various power electronic converters based on the output voltage levels generation and applications [11]. The general PWM methods are available to control power switches like single pulse PWM, multiple pulse PWM, trapezoidal method, sinusoidal pulse width modulation and space vector modulation [12, 13].

In this proposed work describes the simulation and modelling of parallel connected VSI inverter using multi-carrier based sinusoidal PWM technique. From this three level inverter output voltages were obtained from parallel connected VSI inverter instead of using multilevel inverter or two level dual VSI inverter, which utilize the single dc voltage source and provides supply to both VSI inverters by using parallel connection. Pulses for the power switches were generated by comparing the sinusoidal signals with multi carrier signals. The proposed method simulated using matlab/simulink.

# 2. Parallel Connected VSI Inverter Topology

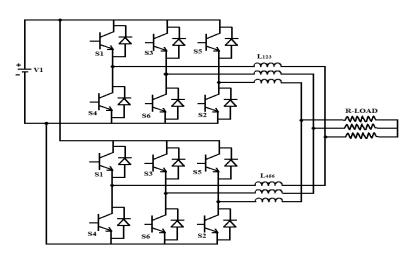

The parallel connected VSI inverter (which is shown in Figure 2) topology used to obtain the 3-level output voltage without utilizes any multilevel inverters or any dual inverter system [14,15]. The main benefit of the system is which consist of only single dc source and it is shared by both VSI inverters [16-18]. Each VSI inverter is operated under on the eight switching modes, in that six switching modes are active vector and two switching modes are zero vector. For example the active switching mode 2(+ + --), which shows the switches S1, S3 & S2 are kept in ON and the switches S4, S5 & S6 are in OFF condition. And the zero switching mode 8(- - -)shows the switches S2, S4 & S6 are in ON and the switches S1, S3 & S5 are in OFF condition, which is shown in Table 1. Similarly the parallel connected VSI inverter operated under eight switching modes based on the firing pulse generation by using multi carrier based sinusoidal PWM method. The stepped output voltage generated from the parallel connected VSI inverter, which is converted into sinusoidal output voltage using split inductor and it is connected to three phase R load connection.

Figure 2. Single dc source based parallel connected VSI inverter

| ле | T. Switching wodes for Parallel Connected v31 m   |                    |

|----|---------------------------------------------------|--------------------|

|    | VSI level inverter-1 & inverter-2 switching modes |                    |

|    | Switching Vectors                                 | Switches Turned ON |

|    | 1 (+ + +)                                         | S1, S3, S5         |

|    | 2 (+ + -)                                         | S1, S3, S2         |

|    | 3 (+ - +)                                         | S1, S6, S5         |

|    | 4 (+)                                             | S1, S6, S2         |

|    | 5 (- + +)                                         | S4, S3, S5         |

|    | 6 (- + -)                                         | S4, S3, S2         |

|    | 7 ( +)                                            | S4, S6, S5         |

|    | 8 ()                                              | S4. S6. S2         |

Table 1. Switching Modes for Parallel Connected VSI Inverter

The output voltages from the parallel connected VSI inverter are Vao, Vbo and Vco. The voltage Vp is the pinch of voltage, which is the addition of maximum and minimum range of three phase voltage values are Van, Vbn & Vcn (phase to neutral voltage).

$$V_{a0} = V_{an} - V_p \tag{1}$$

$$V_{b0} = V_{bn} - V_p \tag{2}$$

$$V_{c0} = V_{cn} - V_p \tag{3}$$

$$V_{p} = \frac{\max(V_{an}, V_{bn}, V_{cn}) + \max(V_{an}, V_{bn}, V_{cn})}{2}$$

(4)

These voltage ranges are obtained based on the variation of the multi carrier based sinusoidal pulse width modulation.

#### 3. Multi-Carrier Based Sinusoidal PWM Technique

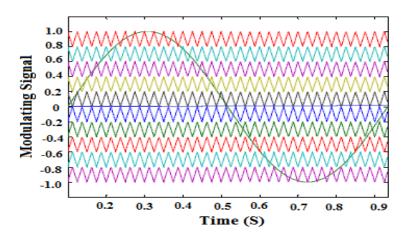

SPWM algorithm is one of the mostly used pulse width modulation (PWM) used to control power switches placed in any power converter topology, which engender the switching pulses by evaluate the reference signals (sinusoidal signals) with multi carrier signals is shown in Figure 3. Here totally 10 carrier signals are compared with sinusoidal waveform to generate the firing pulses for parallel connected VSI inverter.

Figure 3. Multi-carrier based sinusoidal PWM technique

The modulating frequency of the multi carrier signal is verified based variation of amplitude and time period change. The modulating frequency of the carrier signal ( $m_t$ ) is,

$$m_t = \frac{A_1}{(m-1)A_2}$$

(5)

Then the amplitude modulation of the multi carrier signals are based on the ratio of  $f_{c1}$  to  $f_{c2}$ ,

$$m_{a1} = \frac{f_{c1}}{f_{m1}}$$

(6)

Based on the amplitude, switching frequency and modulating frequency of multi carrier signals, this is compared with full sinusoidal signal (with positive & negative cycle). Based on this gating pulses the parallel connected VSI inverter can be controlled.

# 4. Simulation Results and Discussion

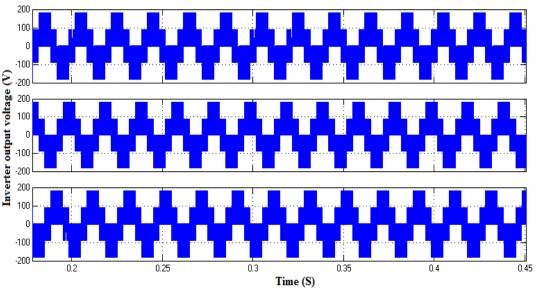

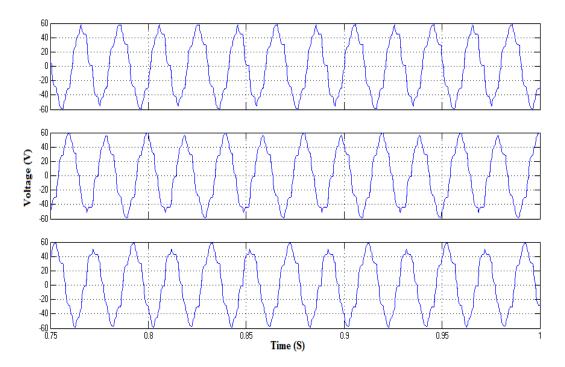

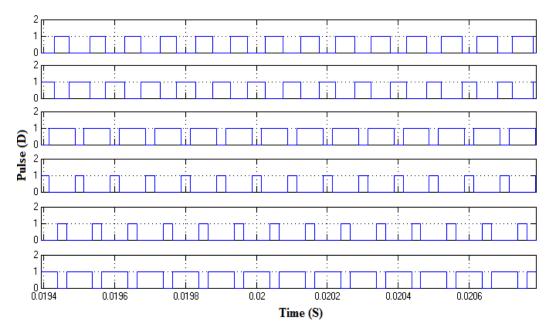

This system easily accomplished at this point largely focus on production of 3-level output voltage with the help of parallel connected VSI inverter instead of using multilevel inverter or dual connected inverter, which reduces the conduction loss, voltage stress and avoids capacitor balancing problem and which is replicated using matlab/simulimk 11b. In Figure 4 shows the 3-level output voltage with parallel connected VSI inverter and sinusoidal output voltage after the split inductor is shown in Figure 5. In Figure 6 shows the pulse generation is based on multi carrier based sinusoidal pulse width modulation to control the parallel connected VSI inverter.

Figure 4. 3-level output voltage with parallel connected VSI inverter

Figure 5. Sinusoidal output voltage after the split inductor

Figure 6. Gate pulse generation for VSI inverter1

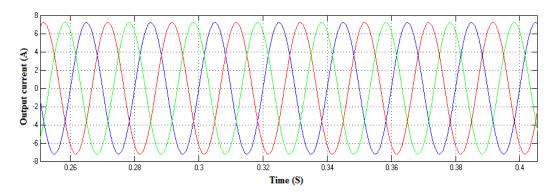

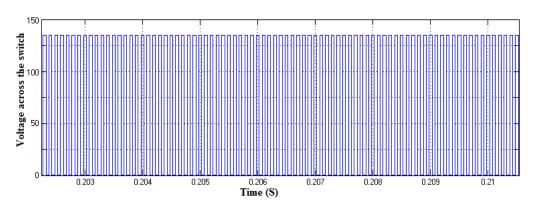

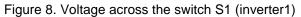

Controlled output current from parallel connected VSI inverter is shown in Figure 7. And in Figure 8 shows the voltage across the switch S1 in VSI inverter 1.

Figure 7. Controlled output current from parallel VSI inverter

Parallel Connected VSI Inverter Using Multi-Carrier Based Sinusoidal .... (D. Karthikeyan)

#### 5. Conclusion

This paper proposes the Parallel connected VSI inverter using multi-carrier based sinusoidal PWM technique to produce three level output voltage without using multilevel inverter or any dual converter concept. From this method, the improved output voltage with better current control was achieved. The proposed method reduces the voltage stress in the power switches and minimises the total harmonic content in the circuit. The parallel connected VSI inverter was controlled by using multi carrier SPWM method, which produces better control compare to conventional PWM methods.

#### References

- [1] D Divan, H Johal. A smarter grid for improving system reliability and asset utilization. Proc. IEEE 5th Int. Power Electron. Motion Control Conf. 2006: 1–7.

- [2] JM Carrasco, JT Bialasiewicz, E Galv´an, RCP Guisado, MAM Prats, JI Leo´n, NM Alfonso. Powerelectronic systems for the grid integration of renewable energy sources: A survey. *IEEE Trans Ind. Electron.* 2006; 53(4): 1002–1016.

- [3] R Palanisamy, AU Mutawakkil, K Vijayakumar. Hysteresis SVM for coupled inductor z source diode clamped 3-level inverter based grid connected PV system. *International Journal of Power Electronics and Drive Systems*. 2016; 7(4).

- [4] M Glinkowski, G Rackliffe. Advances in wind energy technologies the context of smart grid. *Proc. IEEE*. 2011; 99(6): 1083–1097.

- [5] PC Loh, DM Vilathgamuwa, YS Lai, GT Chua, YW Li. Pulse width modulation of Z-source inverters. *IEEE Trans. Power Electron.* 2005; 20(6): 1346–1355.

- [6] CJ Gajanayake, LF Lin, SP Hoay, SL Kian. Extended boost of Z-source inverters. *IEEE Trans. Power Electron*. 2010; 25(10): 2642–2652.

- [7] F Gao, L Poh, RC Teodorescu, F Blaabjerg. Diode-assisted buck-boost voltage-source inverters. IEEE Trans. Power Electron. 2009; 24(9): 2057–2064.

- [8] F Gao, PC Loh, F Blaabjerg. Asymmetrical and symmetrical embedded of Z-source inverters. IET Power Electron. 2011; 4(2): 181–193.

- [9] F Gao, PC Loh, FR Blaabjerg, DM Vilathgamuwa. Five-level based Z-source diode-clamped inverter. *IET Power Electron.* 2010; 3(4): 500–510.

- [10] AH Rajaei, M Mohamadian, SM Dehghan, A Yazdian. Single phase induction motor drive system using Z-source inverter. *IET Electr. Power Appl.* 2010; 4(1): 17–25.

- [11] M Hanif, M Basu, K Gaughan. Understanding the operation of a Z-source inverter of photovoltaic application with the design example. *IET Power Electron.* 2011; 4(3): 278–287.

- [12] R Palanisamy, K Vijayakumar, Maximum Boost Control for 7-level z-source cascaded h-bridge inverter. *International Journal of Power Electronics and Drive Systems*. 2017; 8(2).

- [13] B Gultekin, M Ermis. Cascaded multilevel converter-based transmission STATCOM: System design methodology and development of a 12 kV 12 MVAr power stage. *IEEE Trans. Power Electron.* 2013; 28(11): 4930–4950.

- [14] W Jin, FZ Peng. Unified power flow controller using cascade multilevel inverter. IEEE Trans. Power Electron. 2009; 19(4): 1077–1084.

- [15] P Lezana, J Pou, TA Meynard, J Rodriguez, S Ceballos, F Richardeau. Survey on fault operation on multilevel inverters. *IEEE Trans. Ind. Electron.* 2010; 57(7): 2207–2218.

- [16] WC Song, AQ Huang. Fault-tolerant design and control strategy of cascaded H-bridge multilevel converter-based STATCOM. *IEEE Trans. Ind. Electron.* 2010; 57(8): 2700–2708.

- [17] WP Zhang, DH Xu, PN Enjeti, HJ Li, JT Hawke, HS Krishnamoorthy. Survey on fault-tolerant techniques for power electronic converters. *IEEE Trans. Power Electron.* 2014; 29(12): 6319–6331.

- [18] R Palanisamy, K Vijayakumar, A Bagchi, V Gupta, S Sinha. Implementation of Coupled Inductor Based 7-Level Inverter with Reduced Switches. *International Journal of Power Electronics and Drive Systems*, 2017; 8(3).

#### **Biographies of Authors**

D. Karthikeyan received B.E Degree in EEE from A.I.H.T College, Affiliated to Anna University, Tamil Nadu, India in 2009, and received the M.Tech degree in Power Electronics and Drives from SRM University, Kattankulathur, Tamilnadu, India in 2013. And pursuing PhD degree in the area of Multiport converter. Presently working as Assistant Professor in the Department of Electrical Engineering, SRM University, Kattankulathur, and Chennai, India. His research interests include Power Electronics Multilevel inverters, AC drives, DC drives, multi level inverter.

R. Palanisamy received B.E Degree in EEE from M. Kumarasamy engineering college (Anna University Coimbatore), Karur, Tamil Nadu, India in 2011 and received M.Tech degree in Power Electronics and Drives from SRM University, Kattankulathur, Tamilnadu, India in 2013. And pursuing PhD degree in the area of Z source inverter with 3D-SVM. Presently working as Assistant Professor in the Department of Electrical Engineering, SRM University, Kattankulathur, and Chennai, India. His research interests include Power Electronics Multilevel inverters, Various PWM Techniques and grid connected Photovoltaic system.

K. Vijayakumar received B.E degree in Electrical and Electronics Engineering and M.E degree in Power System Engineering both from Annamalai University, Tamil Nadu, India. & received P.hD in congestion Management in Deregulated Power systems from SRM University, Kattankulathur, Tamilnadu, India in 2013. His research interests include Power system: Deregulation, Modeling, Control and Operation, Optimization, FACTS, Power Quality. Presently working as Professor and Head of Department of Electrical & Electronics Engineering, SRM University, Kattankulathur, and Chennai, India.

D. Selvabharathi received B.E Degree in EEE from Valliammai Engg college, Affiliated to Anna University, Tamil Nadu, India in 2007, and received the M.Tech degree in Power Electronics and Drives from SRM University, Kattankulathur, Tamilnadu, India in 2012. And pursuing PhD degree in the area of Multiport converter. Presently working as Assistant Professor in the Department of Electrical Engineering, SRM University, Kattankulathur, and Chennai, India. His research interests in FACTS & Power Quality.